Основной идеей, дающей начало нашим исследованиям, была разработка быстродействующего программно-определяемого радиоприемника (ПОР), обеспечивающего возможность переконфигурирования во время работы. Для реализации описанных выше функциональных возможностей было предложено использовать аппаратные возможности программируемых логических интегральных схем (ПЛИС).

Суть технологии программно-определяемого радио заключается в том, что базовые параметры приёмопередающего устройства определяются именно программным обеспечением, а не аппаратной конфигурацией, как принято в классических конструкциях. Если говорить более точно, то программно-определяемая радиосистема (англ. Software-defined radio, SDR) это радиопередатчик и/или радиоприемник, использующий технологию, позволяющую с помощью программного обеспечения устанавливать или изменять рабочие радиочастотные параметры, включая диапазон частот, тип модуляции или выходную мощность, за исключением изменения рабочих параметров, используемых в ходе обычной предварительно определенной работы с предварительными установками радиоустройства, согласно той или иной системе. [1, с.1]

Одна из первых систем ПОР под названием SpeakEasy разрабатывалась американскими военными. Основной целью проекта была эмуляция более 10 существующих военных радиосистем, функционирующих в диапазоне от 2 до 20 МГц, с помощью программной обработки. SpeakEasy позволяла цифровой аппаратной платформе общего назначения связываться с другими системами в широких диапазонах частот, применяя различные виды модуляции, методы кодирования данных, а так же варьировать другими параметрами. [1, с.2]

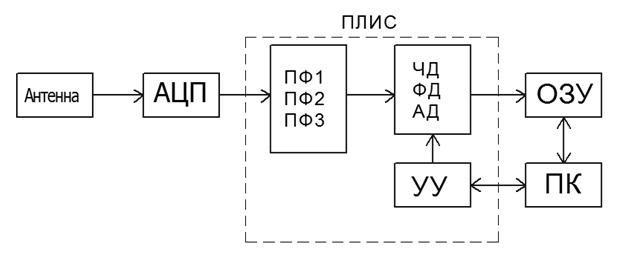

Классическая система ПОР содержит антенну, блоки аналого-цифрового, цифро-аналогового преобразования, цепи обработки цифровых сигналов и другие вспомогательные блоки. Как правило, вся цифровая обработка сигналов может вестись как на процессорах общего назначения, так и с помощью схем, реализованных на ПЛИС или специализированных ИМС. Решения на ПЛИС и специализированных микросхемах намного (в десятки и сотни, а иногда и тысячи раз) более экономичны с точки зрения энергопотребления. Применение ПЛИС также позволяет оперативно переконфигурировать систему в режиме реального времени. На рисунке 1 представлена структурная схема программно-определяемого приемника на ПЛИС.

Описанная ниже структура реализуется на ПЛИС LX50T семейства Virtex-5 компании Xilinx, которая установлена на специальной отладочной плате Genesys от компании Digilent.

Рисунок 1. Структурная схема ПОР на ПЛИС

Система работает следующим образом: сигнал с антенны напрямую поступает в аналогово-цифровой преобразователь (АЦП), затем оцифрованный сигнал поступает в ПЛИС, где заранее программно реализованы полосовые фильтры (ПФ1, ПФ2, ПФ3), частотный, фазовый и амплитудный детекторы (ЧД, ФД, АД) а также устройство управления (УУ). Внутри ПЛИС синтезируется программное процессорное ядро, которое через шину данных позволяет управлять всеми этими элементами внутри схемы. После этого информационный цифровой сигнал от ПЛИС поступает в оперативную память (ОЗУ), после чего устройство управления подает сигнал на персональный компьютер (ПК) для считывания им информации из ОЗУ.

Список литературы:

- Википедия [Электронный ресурс] // Программно-определяемая радиосистема. URL: https://ru.wikipedia.org/wiki/Программно-определяемая_радиосистема (дата обращения: 21.05.2015)

- Галкин В.А.Основы программно-конфигурируемого радио.

- Olympus [Электронный ресурс] URL: https://www.olympus-ims.com/ru/ (дата обращения: 14.03.2015)

- Проектирование автоматизированных систем измерения, контроля и управления РЭС: Казань: Изд-во Казань. гос. техн. ун-та, 1999.[schema type=»book» name=»СИСТЕМА ПРОГРАММНО-ОПРЕДЕЛЯЕМОГО РАДИО НА БАЗЕ ПЛИС» description=»Цель настоящего исследования — повысить быстродействие, скорость переконфигурации а также снизить энергозатраты системы программно-определяемого радио (от англ. Software — defined radio, SDR), применяя в качестве блока обработки сигналов схему, построенную на базе программи́руемой логи́ческой интегра́льной схе́мы (ПЛИС). Метод проведения исследования заключается в совокупном применении официального программного обеспечения Xilinx ISE Design Suite от компании Xilinx и ПЛИС LX50T семейства Virtex®-5 той же компании, которая реализована на специальной отладочной плате Genesys™ от компании Digilent. Результат: разработка данной системы еще не окончена, но в ходе данного исследования нам удалось синтезировать процессорное ядро внутри ПЛИС, разработать структурную и функциональную схемы устройства.» author=»Каллаур Валентин Олегович, Сафин Булат Галимзянович, Зуев Олег Юрьевич» publisher=»БАСАРАНОВИЧ ЕКАТЕРИНА» pubdate=»2017-03-13″ edition=»ЕВРАЗИЙСКИЙ СОЮЗ УЧЕНЫХ_30.05.2015_05(14)» ebook=»yes» ]